## Introduction to Xilinx Spartan-3E Starter Kit

Steve Knapp Sr. Applications Manager Scott Schlachter

Sr. Systems Engineer

### Agenda

- Overview

- Memory / Configuration Features

- Connectivity Features

- Misc. Features

- Documentation, Software, Reference Designs

- Summary

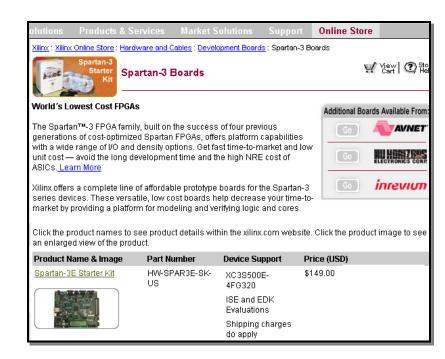

#### **Spartan-3E Starter Kit Overview**

- A full-featured Spartan-3E FPGA development board solution

- Instant access to the full capabilities of the Spartan-3E FPGA family

- Complete kit includes

- Starter Kit Board

- Power Supply

- Evaluation Software & Resource CD

- USB Cable (for programming)

- International versions available

Resale: US\$149

www.xilinx.com/s3estarter

Order from Xilinx Online Store, or your local Xilinx Distributor

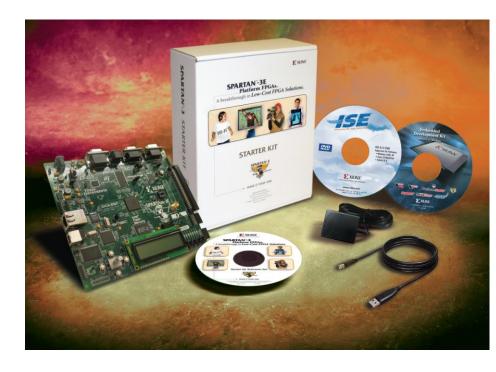

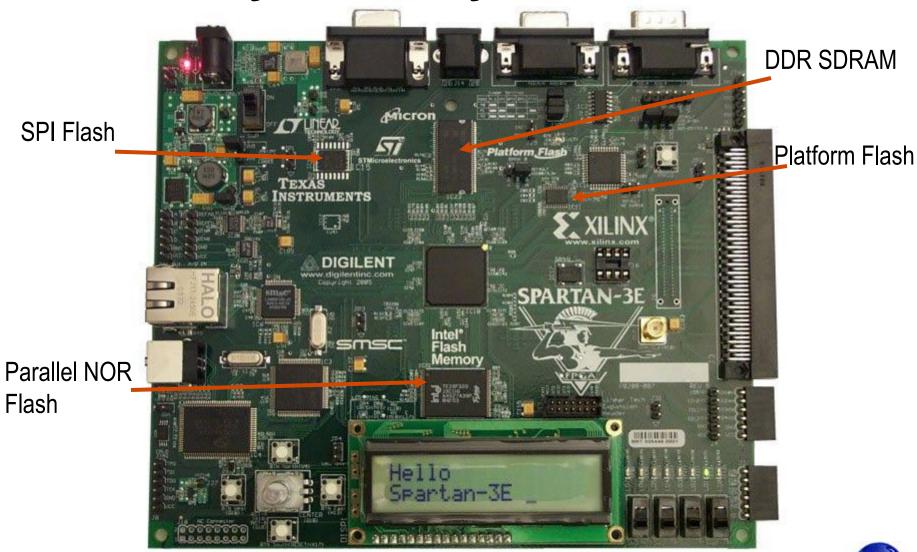

#### **Starter Kit Board Features**

#### Xilinx Devices

- Spartan-3E XC3S500E-4FG320

- CoolRunner-II XC64-VQ44

#### Memory

- Xilinx Platform Flash XCF04S-VO20

- 128Mbit Intel<sup>®</sup> StrataFlash

- 16Mbit STMicro® SPI serial Flash

- 32Mx16 (64Mbytes) Micron<sup>®</sup> DDR SDRAM

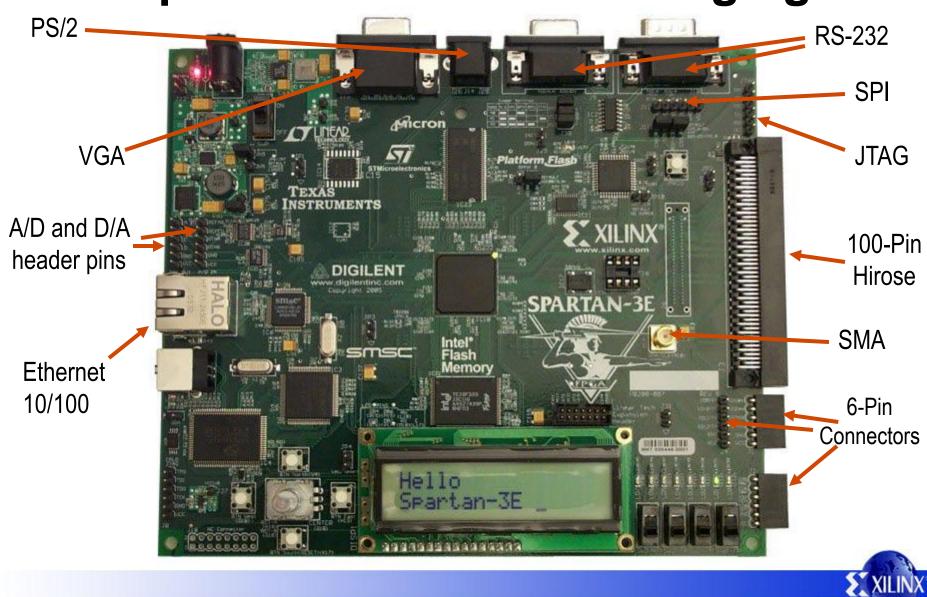

#### Connectivity

- Xilinx Embedded USB Programming Capability

- SMsC<sup>™</sup> Ethernet 10/100 PHY

- 100-Pin Hirose Expansion Connector

- Three 6-Pin Expansion Connectors

- VGA, RS-232, PS/2, SMA

#### Other

- 50 MHz Oscillator

- Rotary Encoder, Four Momentary-Contact Push Buttons, Four Slide Switches

- 16 Character 2-Line LCD, 8 LEDs

- A/D and D/A

- Secure EEPROM

#### Xilinx Devices

- Spartan-3E, XC3S500E-FG320

- 232 user I/O: 176 Bidirectional, 56 Input-only arrange in 4 I/O Banks

- 4 DCMs, 20 BRAM blocks, 1,164 CLBs

- Pin compatible with larger-density XC3S1200E or 1600E

- CoolRunner<sup>™</sup>-II, XC2C64A-VQ44

- Used for glue logic for the configuration circuitry. Can be used for more complex board functions, such as a "Configuration-Watchdog Timer" or similar controller for ISP functions.

- Platform Flash, XCF04S-VO20

- One of three possible FPGA configuration storage devices

- Extra 1.8Mbits provided for possible code or data storage

- Embedded Platform USB Cable Circuit

- Simple standard USB cable (included) for all JTAG operations with the Xilinx ISE tools: iMPACT, Chipscope, and EDK

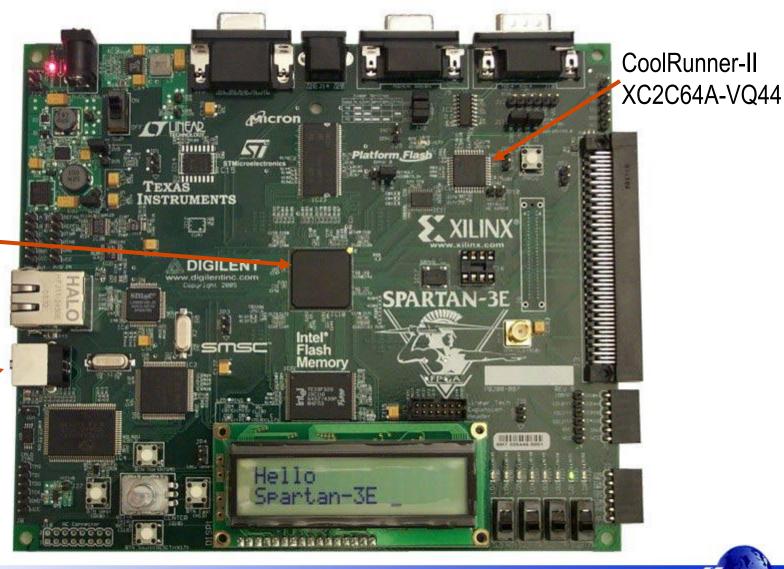

#### Spartan-3E FPGA & CoolRunner-II CPLD

Spartan-3E XC3S500E-FG320

USB for JTAG operations

#### **Easy Memory Interfaces**

XILINX

Flash

#### Spartan-3E Excels at Bridging

#### **Complete Documentation**

- Getting Started

- 3 quick and easy steps to jumpstart your design

- 164-page User's Guide

- Complete technical manual on all features and capabilities

- Delivered via web www.xilinx.com/s3estarter

#### **Evaluation Software Included**

- 60-Day Evaluation Licenses for Full-Featured Tools

- ISE Foundation is the Xilinx complete logic design environment

- The Embedded Development Kit (EDK)

bundle is an integrated software solution for

creating MicroBlaze-based embedded

processing systems

- Free ISE WebPACK

- ISE WebPACK offers HDL synthesis and simulation, implementation, device fitting, and JTAG programming

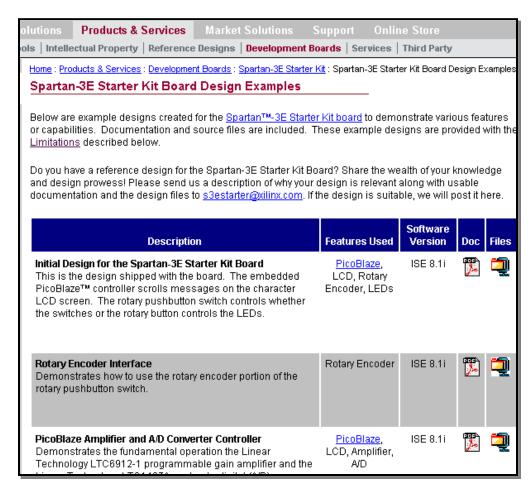

## "How To", "Can Do" Reference Designs

- Demonstrates various features and capabilities

- LCD display control

- StrataFlash, SPI programmer

- Rotary encoder interface

- Frequency counter

- PicoBlaze examples

- MicroBlaze examples

- And more ...

- Documentation and source files are included

- Linked from www.xilinx.com/s3estarter

## Demonstrating New Features and Improved Capabilities

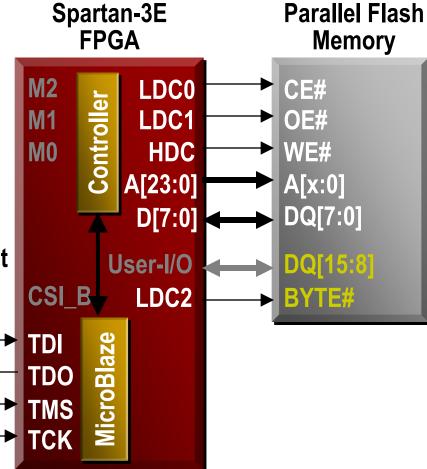

- Spartan-3E FPGAs configure from commodity Flash memory

- Fully supports easy-to-use Xilinx Platform Flash

- SPI serial Flash

- Parallel NOR Flash support primarily for MicroBlaze embedded applications

- Improved support for embedded systems applications

- Low-end support for 32-bit MicroBlaze RISC core

- Efficient 8-bit PicoBlaze controller core

- Low-cost, space efficient FPGA power solution from Texas Instruments

### Agenda

- Overview

- Memory & Configuration Features

- Connectivity Features

- Misc. Features

- Documentation, Software, Reference Designs

- Summary

#### **Memory: DDR SDRAM**

- Micron MT46V32M16TG-6TF (512Mbit)

- 32M-deep, 16-bit data path

- 66-pin TSOP package

- Industry standard package, can drop in up to 1GB device

- Simple point-to-point series termination

- DDR SDRAM requires 2.5V

- Spartan-3E FPGAs have four I/O banks to support different I/O standards

- FPGA I/O Bank 3 dedicated for this purpose

- Voltage supply to FPGA I/O Bank 3 and DDR SDRAM provided by 2.5V switching regulator

#### **Configuration Features (cont.)**

- Xilinx Platform Flash

- XCF04S-VO20 connected for MS mode

- Extra space for design/code storage XAPP482, XAPP544, XAPP694

- 2<sup>nd</sup> XCF04S-VO20 Footprint to allow for two XCF04S in series for configuration of optional XC3S1600E drop-in

- Parallel NOR x8/x16 Flash PROM

- Intel StrataFlash 128Mbit Flash PROM, upgradeable to 256Mbit

- Extra space for design/code storage

- Wired to allow CPLD to optionally control multiple configurations

- CPLD controls A20-A24, but also connected to S3E general IO

- A0-A19 controls only the lowest 8Mbit which is enough for Multiboot for XC3S500E (2.624Mbits) or 1200E (3.833Mbits), and single boot of XC3S1600E (5.958Mbits)

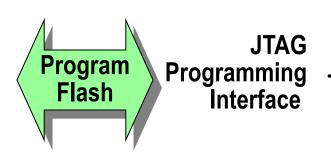

## Configuring the Intel StrataFlash™ Parallel NOR Flash PROM

- Xilinx EDK Flash Memory Programming utility

- Included CD

- Xilinx PicoBlaze RS-232 StrataFlash™ Programmer reference design

- Available at <u>www.xilinx.com/s3estarter</u>

## Flash Memory Programmer

In EDK 8.1, use the Base System Builder Wizard to build a MicroBlaze design w/the Flash PROM controller – Flash Memory Programmer utility is built in to EDK!

See Chapter 9, "Flash Memory

Programming" in the *Embedded System*Tools Reference Manual

(http://www.xilinx.com/ise/embedded/est

\_rm.pdf)

# Configuring the STMicroelectronics SPI Flash PROM

- Available now: PicoBlaze SPI Flash

Programmer for the Spartan-3E Starter Kit Board

- Available at <u>www.xilinx.com/s3estarter</u>

- Coming soon: SPI programming support in the upcoming 8.2i rev of the Xilinx ISE iMPACT configuration tool

- For STMicroelectronics and Atmel Flash PROMs only

## Agenda

- Overview

- Memory / Configuration Features

- Connectivity Features

- Misc. Features

- Documentation, Software, Reference Designs

- Summary

#### **Ethernet PHY**

- Ethernet 10/100 PHY IC

- SMSC LAN83C185

- High Perf, Low Power

- TQFP-64

- Standard MII Port

Single Port 10Base-T RJ-45 Connector w/LEDs

Halo HFJ11

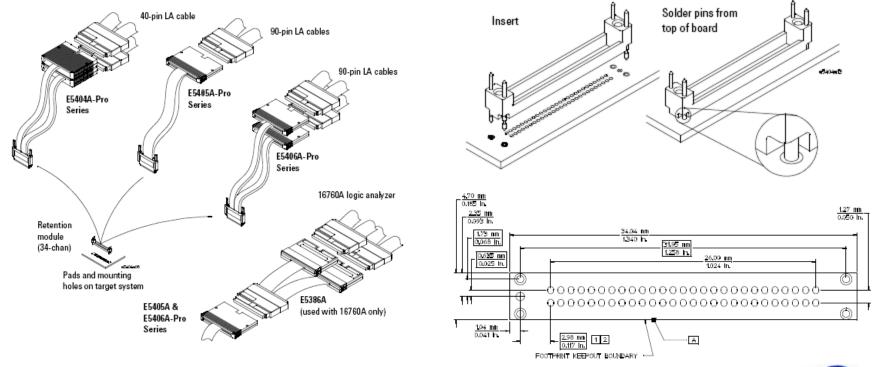

#### **ChipScope Board Connectors**

- ChipScope™ Connector Landing

- Agilent 5404/6A Pro Series Probes with Soft Touch connector, or Tektronix P69xx Probe Modules with D-Max technology

- Industry Standard (between the two so far)

- 16 FPGA IOs shared with FX2 Connector

#### **Hirose FX2 Board Connectors**

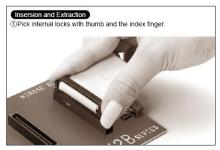

#### Hirose FX2 edge-connector

- Male, right-angle, 100-pin edge connector, 500mA/pin

- Reasonable performance 45mOhms max at 100mA

- Versatile

- Board-to-board connectors available

- Board-to-cable connectors (and cables) available

- www.hirose-connectors.com

- Inexpensive!

- 38 IO (3 on GCLK pins) + 5 Input-only.

- 15 are differential IO, and 2 are differential Input-only

- Possible to do 8 channel differential input+clock, 8 channel output

- Pins take up most of Bank0

- 741G125 tristateable buffer allows for off-board connection into JTAG chain

#### 6-pin Connectors

- Three 0.1" 1x6 Header Pin Connectors

- 1 male straight-lead, 2 female right-angle edge connectors

- Signals: IO/IO/IO/IO/Gnd/Vcc3v3

- Can be used as test points, or a way to bridge to another board using cables/flying leads

- Digilent sells a variety of very inexpensive daughter boards (Peripheral Modules) that can plug in:

- Dual 12bit A/D, Dual 8bit D/A, Dual H-Bridge Amps, Amplified Speaker board, 4 Pushbuttons, 4 Slide switches, RS232, 4 Open Collector, 4 Digital Input (w/Schmitt-Trigger inv, protection diodes, and debounce filters), 6 Screw-terminals

- ~\$8-\$25, order online at www.digilentinc.com

OD-GON2

#### RS232, VGA, PS2, and SPI

- RS232 Port Connectors

- Maxim MAX3232 3.3V PHY

- Both Female (DCE) DB9 and Male (DTE) DB9

- VGA Port Connector

- Red, Green, Blue, HS, and VS

- Female DB15 Connector

- PS2 Port Connector

- Data, Clock, Ground and 5V

- 8-pin PS2 Connector

- SPI Off-board connector

- 1x6 .1" header connector

### Agenda

- Overview

- Memory / Configuration Features

- Connectivity Features

- Misc. Features

- Documentation, Software, Reference Designs

- Summary

#### **Power Supplies**

- Texas Instruments TPS75003

- Developed for Xilinx Spartan-3 families

- 1.2V Switcher @ 3A

- Solely for Vccint, and has 1x2 header w/jumper, and 1x1 header

- 2.5V LDO @ 300mA

- Solely for Vccaux, and has 1x2 header w/jumper, and 1x1 header

- 3.3V Switcher @3A

- Several devices on board

- Linear LTC3412

- 2.5V Switcher for DDR SDRAM

- Also powers Vcco3 (SDRAM interface), and optional to Vcco0 (for LVDS)

- Resistor divider to provide 1.25 Vref to SDRAM and S3E

- Linear LTC1844ES5

- 1.8V LDO from 3.3V to power CPLD

#### **Clocks**

- 50 MHz LVTTL Oscillator

- Routed to S3E GCLK in Bank 0, and Coolrunner-II

- Osc Socket routed to S3E GCLK in Bank 0

- SMA to S3E GCLK in Bank 0

- 25MHz XTAL for Ethernet Phy

#### A/D, Amp, and D/A

- SPI-compatible A/D

- LTC1407A-1: 14bit 3Msps Sampling ADC, +/-1.25 Input

- Low Power, and also has Nap and Sleep modes

- SPI-compatible Programmable-gain Amplifier (for A/D)

- LTC6912-1: Programmable Gain Amplifier

- 2-ch ideal for amplifying audio into A/D

- Hardware or software shutdown modes

- SPI-compatible D/A

- LTC2624: Quad 12bit DAC

- Separate reference for each DAC, options on board for these

- All on the same SPI bus with the SPI Flash PROM

#### Secure EEPROM and LCD

- Secure EEPROM

- Dallas Semiconductor/Maxim DS2432 (1Kbit protected 1-wire EEPROM with SHA-1 engine)

- XAPP780, security through bitstream authentication

- 2x16 character LCD Display

- Industry standard processor and interface

- Similar to other Xilinx boards

### Agenda

- Overview

- Memory / Configuration Features

- Connectivity Features

- Misc. Features

- Documentation, Software, Reference Designs

- Summary

#### **Application Notes**

- Configuring Spartan-3E Xilinx FPGAs with SPI Flash Memories

- (XAPP445)

- Configuring Spartan-3E from Platform Flash

- Bootloading MicroBlaze from Platform Flash (XAPP482)

- Reading Data from Platform Flash (XAPP694)

- Reading and writing data to Platform Flash (XAPP544)

- Configuring Spartan-3E in BPI mode from Intel StrataFlash

- Configuring S-3E and booting MicroBlaze from the same flash device (XAPP447 – TBD release)

- Multi-Boot configuration (S3E Data Sheet)

- FPGA IFF Copy Protection Using Dallas Semiconductor/Maxim DS2432 Secure EEPROMs (XAPP780)

- Remote FPGA Reconfiguration Using MicroBlaze (XAPP441)

- Using CPLD, DDR SDRAM, and Ethernet port

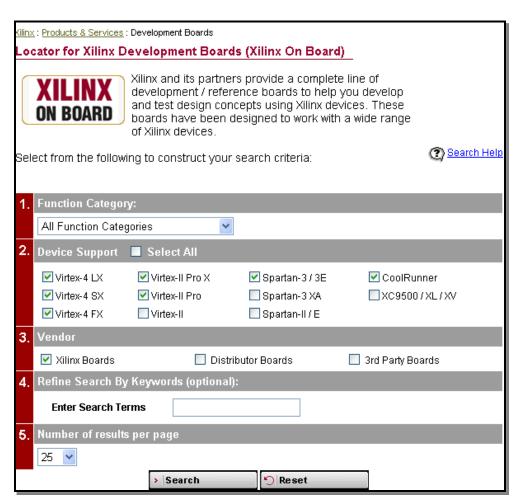

#### More Development Kits Available

- Xilinx On Board

- Complete listing of development and reference boards

- Xilinx, Distributor,

3<sup>rd</sup> Party

www.xilinx.com/xob

#### **Summary**

- The Spartan-3E Starter Kit is the latest low-cost, full featured development platform from Xilinx

- Begin your design today and purchase a Starter Kit at:

- www.xilinx.com/s3estarter

Order thru Xilinx Online Store, or your local Xilinx Distributor